Pong game on Altera FPGA as exercise in Hardware-/Software-Codesign

|

|

4 vuotta sitten | |

|---|---|---|

| images | 4 vuotta sitten | |

| nios2_uc | 4 vuotta sitten | |

| output_files | 4 vuotta sitten | |

| software | 4 vuotta sitten | |

| .gitignore | 4 vuotta sitten | |

| README.md | 4 vuotta sitten | |

| myfirst_niosii.qpf | 4 vuotta sitten | |

| myfirst_niosii.qsf | 4 vuotta sitten | |

| myfirst_niosii.vhd | 4 vuotta sitten | |

| nios2_uc.qsys | 4 vuotta sitten | |

| nios2_uc.sopcinfo | 4 vuotta sitten | |

| output_file.map | 4 vuotta sitten |

README.md

DE2-115-FPGA-Pong

This is a Pong game on an Altera FPGA as an exercise in Hardware-/Software-Codesign.

The video below shows it in action, running on an university-made extension board.

Source files

.

├── myfirst_niosii.vhd

├── nios2_uc

│ ├── nios2_uc.bsf

│ └── synthesis

│ └── nios2_uc.vhd

├── README.md

└── software

├── hello_world

├── hello_world_bsp

├── Pong_Code

│ ├── Display.h

│ ├── Main.c

│ └── structs.h

└── Pong_Code_bsp

Data flow

This diagram shows all the implemented parts and the singnals to connect them. The implementation is split in pysical Hareware, programmable logic as VHDL and instruction based C software.

VHDL program

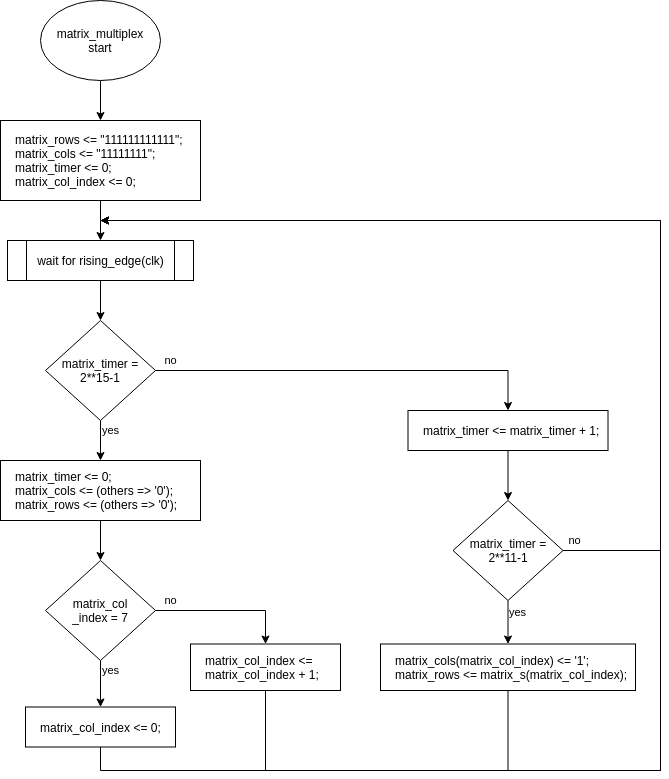

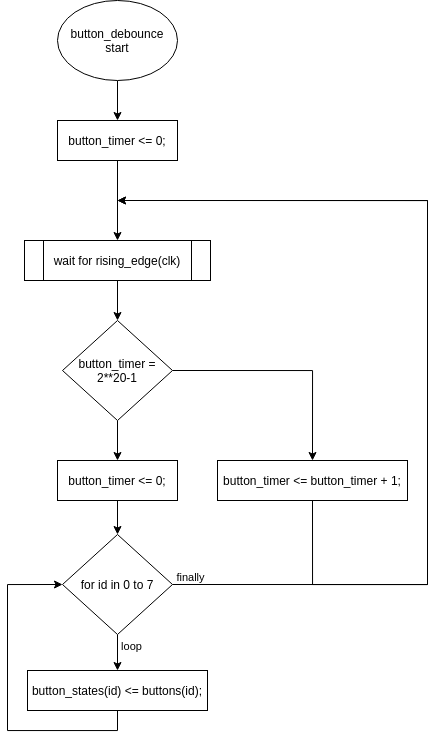

Below are shown the two main processes that are implemented in VHDL. They run simultanously and independent of each other. All processes and the synthesized CPU are connected to a common 50 MHz clock and a reset signal. When reset, all processes are asynchronously forced to output their default values, as seen in the first block.

Multiplex process

The matrix multiplexing timer has been sized regarding the following equations:

- Timer frequency:

50Mhz / 2**20 = 1526 Hz - Time per column:

1 / 1526 Hz = 0.66 ms - 1526 Hz / 8 = 190 Hz matrix refresh rate

Debounce process

Matrix instruction

The matrix instruction contains 20 bits that are split in three parts:

20 16 12 8 4 0

XXXX CCCC RRRR RRRR RRRR

| Symbol | Bit range | Description |

|---|---|---|

| X | 19 downto 16 | unused |

| C | 15 downto 12 | column number |

| R | 11 downto 0 | row data |

The column number can be one of the following values:

- 0000: don't set anything

- 0001: set column 0 to row data

- 0010: set column 1 to row data

- 0011: set column 2 to row data

- ...

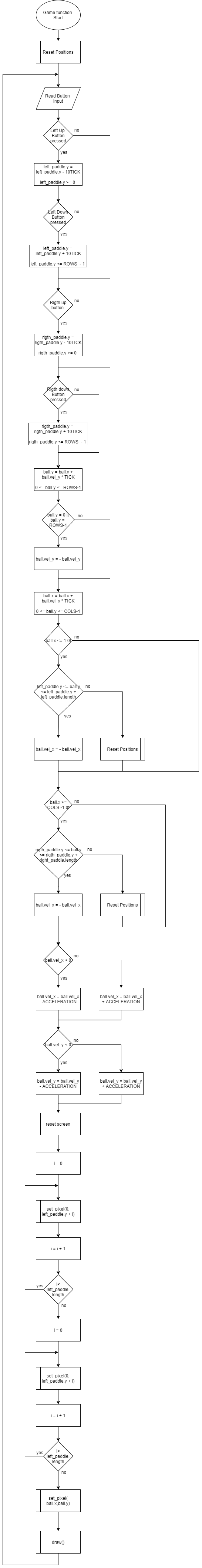

Flowcharts of the C program

Below images show flowcharts for all featured software functions. Fist chart feature the main game function. Subfunctions are described below. See:

Main function Flowchart

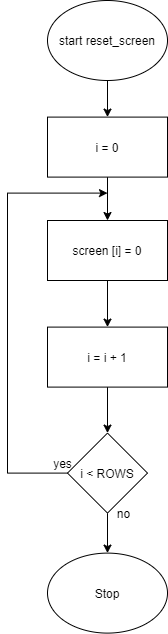

Subfunctions Flowcharts

This is the flowchart of the draw function. This function outputs the virtual screen to the matrix instruction register to be processed by VHDL.

Flowchart of reset_position function. Function to reset positions of both paddles and ball to default. Default positions and values can be adjusted in this function

Flowchart of reset_screen function. Function to reset all pixels of the virtual screen to 0.